史上最牛的嵌入式综合试验开发系统!

[系统结构]

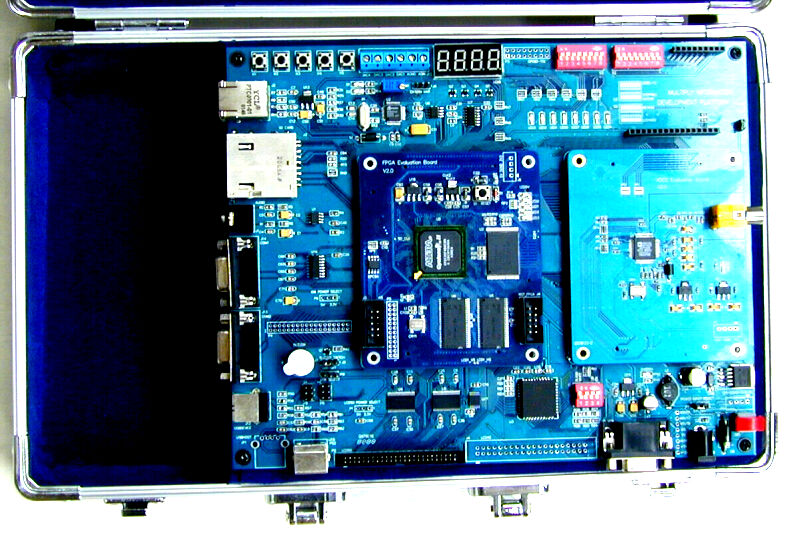

子母板设计,六层板工业级保准设计FPGA子板,两层工业级底板

[硬件资源]

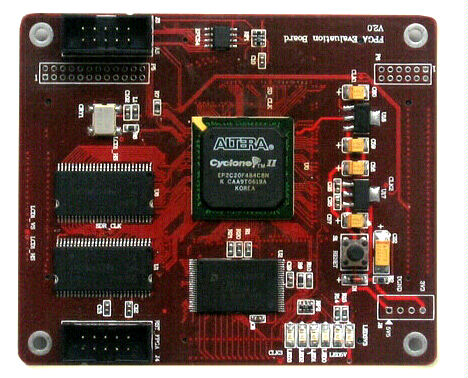

l FPGA子板资源

Ø FPGA芯片:ALTERA Cyclone II

EP2C20F484C8(可选EP2C35F484C8)

Ø 配置芯片:EPCS4(EPCS16) ,EPCS4配置EP2C20,EPCS16配置EP2C35

Ø SDRAM: 16M Byte 高速SDRAM(可选32M

Byte)

Ø FLASH: 4M Byte

Ø SRAM:512K Byte

Ø LED:4

Ø 两种下载配置模式:AS模式和JTAG模式

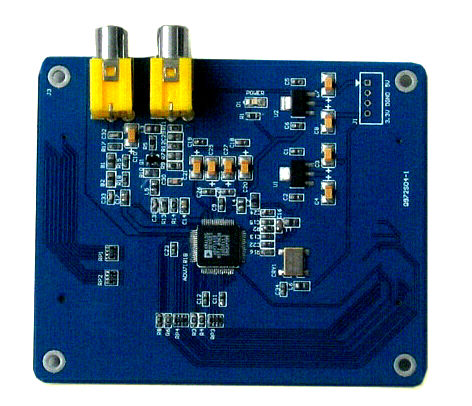

l 视频子板(ADV7181)

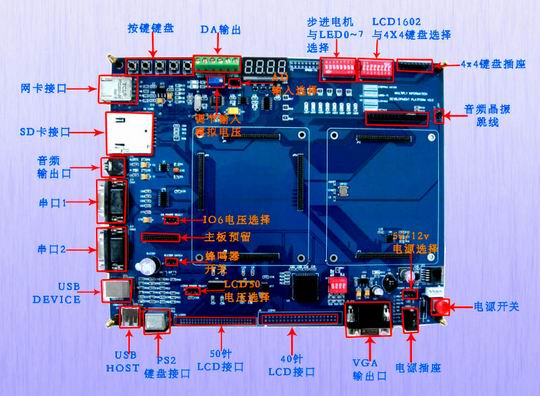

l 底板资源

Ø 2路9针RS-232串口,实现与计算机的数据通信;辅助调试,结果输出

Ø 40针TFT

LCD数字接口

Ø 50针TFT

LCD数字接口(带触摸屏)

Ø VGA接口

Ø 100M网络接口

Ø 100M ETHERNET

PHY网络

Ø 音频DA,双通道立体声输出

Ø 一个交流蜂鸣器

Ø 4位八段数码管

Ø 4个输入键一个复位键

Ø 6个发光二极管

Ø 16*2

LCD接口,标准的字符型液晶模块接口

Ø PS/2鼠标,键盘接口

Ø SD卡接口

Ø USB

host,client接口

Ø CF卡接口

Ø 40针IDE硬盘接口

Ø 6*40针脚2.0mm排针

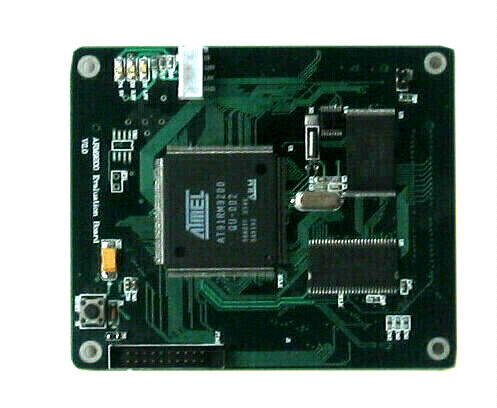

l ARM9200子板资源(选配)

Ø ARM芯片:AT91RM9200

Ø SDRAM: 16M Byte 高速SDRAM

Ø NAND:K9F1208

Ø Nor FLASH:28FXXJ3

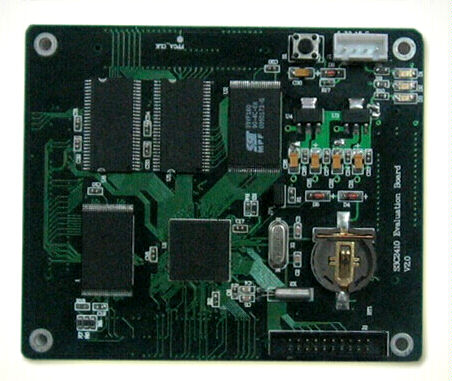

l S3C2410子板资源(选配)

Ø CPU:S3C2410

Ø SDRAM:16M Byte

Ø NAND:K9F1208

Ø Nor FLASH:SST39VF6401

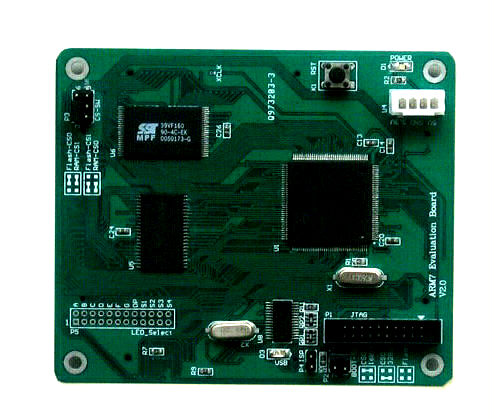

l ARM7子板

CPU:LPC2xxx

[配套软件]

[资料文档]

[NIOS、IP核综合开发实例]

Ø BUTTON中断和处理

Ø 16*2

LCD字符显示

Ø 480*234 TFT

LCD实验

Ø GUI的应用实例和各种GUI控件的实验

Ø RS232串口控制台输出

Ø 数码管驱动

Ø PS2键盘

Ø 基于软核的RTC实验

Ø 简单数字钟

Ø FLASH读写

Ø SRAM控制读写

Ø 简单网络服务

Ø 音频初始化和控制

Ø 双NIOS核硬互斥量保护共享内存通信

Ø uC/OS II 多任务例程

Ø 2D图形加速应用(硬件描画点、线)

Ø SD卡读写

Ø CF卡读写

Ø IDE接口实验

Ø NIOS和S3C2410的通信(需要S3C2410子板)

Ø NIOS和RM9200的通信(需要RM9200子板)

Ø Video视频输入(CVBS接口)

[IP 核设计与开发实例]

Ø PS2 IP

Core(基于AVALON总线)

Ø I2C IP

Core(基于AVALON总线)

Ø RTC IP

Core(基于AVALON总线)

Ø Audio 音频输出IP

Core(基于AVALON总线)

Ø Video 视频采集IP Core

Ø TFT

LCD驱动 IP Core(两个硬件图形显示分层,基于AVALON总线)

Ø 2D 图形加速 IP Core(支持绘点、线,基于AVALO)

FPGA核心板

视频子板( ADV7181)

ARM9200子板

ARM7子板

S3C2410子板

系统布局图

实验箱1 (带8.4寸TFT LCD)

实验箱2

|